## 2022 年 VLSI 技術及電路 IEEE 研討會的技術亮點

2022 年 IEEE VLSI 技術及電路 研討會是頂尖的國際會議,這場國際會議記錄微/奈米積體電子的發展速度、進度和演進,預計於 2022 年 6 月 12 日至 17 日舉辦。聯合研討會將以混合形式在夏威夷舉行,包括在 Hilton Hawaiian Village 現場舉行的現場會議,以提供交流機會,以及隨選會議,讓無法旅行的人可以參加特定的講座和小組討論。

今年的研討會適逢固態電晶體發明第75週年。

這次研討會以**「未來關鍵基礎架構的技術及電路」**為核心主題,活動日程之中整合進階技術發展、創新電路設計及各種應用,協助全球社會轉型為智慧連網裝置、基礎架構及系統的新紀元,改變人類彼此互動的方式。

下列是以此為主題的一些精彩論文介紹:

# 聯合技術及電路焦點

今年先前兩場單獨的技術及電路討論會合併為一場研討會。以下是一些精彩論文,展示技術及 電路領域的共同進步:

## 超越 CMOS 機器學習

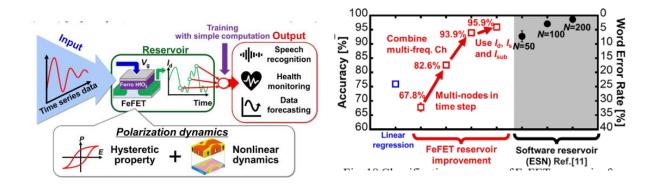

「用於語音辨識的平行資料處理的 HZO/Si FeFET 水庫運算創新方案的實驗示範」-東京大學 (論文 1491)

東京大學的研究人員提出了一種針對語音識別在平行資料處理器中使用鐵電閘門 MOSFET (FeFET) 進行水庫運算的新穎實作。水庫運算是一種機器學習技術,能為邊緣 AI 應用程式提供高效率的線上學習,因為其只包含一層需要訓練的讀出權重。研究人員證明了 FeFET 的極化動力學可以在記憶體作業中執行運算。透過使用從單一 FeFET 漏極電流的時間回應中提取的虛擬節點,已成功執行基本的機器學習任務,例如短期記憶 (STM) 和同位檢查 (PC) 任務。在報告的語音辨識實驗中,達到超過 95.9% 的準確率。

標題:東京大學提出一種針對語音識別 (左) 在平行資料處理器中使用鐵電閘門 MOSFET (FeFET) 進行水庫運算的新穎實作,展現與軟體型水庫運算 (右) 類似的準確度。

## 量子運算

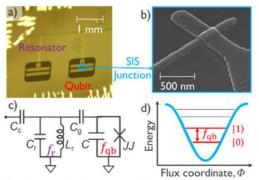

「用於高傳真超導量子位元測量在 10mK 下運作的可擴展式 1.4μW 低溫 CMOS SP4T 多路復用器」 – KU Leuven (論文 1216)

KU Leuven 的研究人員報告在 10mK 基礎溫度下運作的超低功耗低溫 CMOS 單投四擲 (SP4T) 射頻多路復用器的電氣效能。研究人員首次使用多路復用器對超導量子比特進行基準 測試,取得高於 35µs 的量子位元相干時間,以及 99.93% 的平均單量子位元閘極傳真度,超過基於表面代碼的量子糾錯所需的閾值。這項技術證明了超導量子位元在基礎溫度下與超低功耗低溫 CMOS 裝置的可操作性,為進階共同整合方案鑑定基礎。

**Fig. 4** a) Optical image of the qubit chip. b) SEM image of overlap superconductor-insulator-superconductor (SIS) Josephson junction (JJ). c) Equivalent circuit of the resonator-qubit system. d) Potential profile and qubit energy levels.

**Fig. 4** a) Optical image of the qubit chip. b) SEM image of overlap superconductor-

**圖 4** a) 量子位元晶片的光學影像。b) 重疊超導體-絕緣體-超導體 (SIS) 約瑟夫森結

insulator-superconductor (SIS) Josephson junction (JJ). c) Equivalent circuit of the resonator-qubit system. d) Potential profile and qubit energy levels.

(JJ) 的 SEM 影像。c) 諧振器-量子位元系統 的等效電路。d) 電位分佈和量子位元能量 級。

圖檔:1216

標題:由耦合到超導諧振器 (最左側面板)的高相干超導量子位元以及用戶設計的低功耗 RF SP4T 低溫多路復用器 (右側面板)的內部架構組成的量子裝置。

#### 記憶體內運算

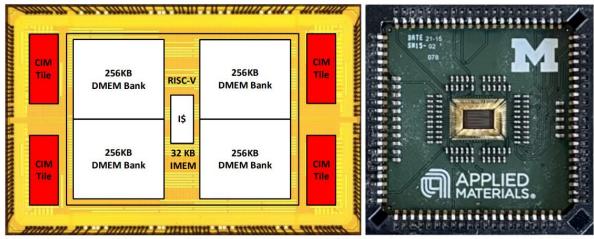

「基於 8 位元 20.7 TOPS/W 多級單元 ReRAM 的運算引擎」 – 密西根大學 (論文 1421)

密西根大學的研究人員與 Applied Materials 合作報告指出,具有多級單元電阻 RAM (ReRAM) 的記憶體類比運算有望為機器學習和科學運算提供高密度和高效率的運算。作者展示了 SoC 原型,該原型由四個獨立的 ReRAM 技術記憶體運算區塊和一個 RISC-V 主機組成。測得的原始和歸一化峰值效率分別為 20.7 和 662 TOPS/W,報告的運算密度為 8.4 TOPS/mm²,使用 128 MNIST 資料集的分類準確率為 96.8%。

Fig. 9. Die micrograph and prototype chip on custom substrate PCB in PLCC socket. Prototype die measures 3.2 x 5.1mm.

Fig. 9. Die micrograph and prototype chip on custom substrate PCB in PLCC socket. Prototype die measures 3.2 x 5.1mm.

圖 9. PLCC 插座中自訂基板 PCB 上的晶片顯微圖像和原型晶片。原型模具尺寸為 3.2 x 5.1 mm。

圖檔:1421

標題:具有多級單元 (MLC) ReRAM 的記憶體內類比運算,有望為機器學習和科學運算提供高密集和高效率的運算支援。展示的是 SoC 原型,該原型由四個獨立的 ReRAM 技術 CIM 區塊和一個 RISC-V 主機組成。測得的原始和歸一化峰值效率分別為 20.7 和 662 TOPS/W。運算密度為 8.4 TOPS/mm2。

#### 記憶體內運算

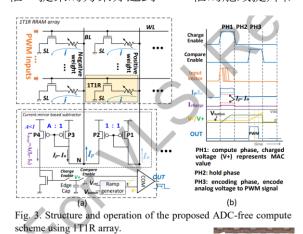

「具有子陣列之間脈寬調變的 40nm 類比輸入無 ADC 記憶體內運算 RRAM 巨集」— 喬治亞理工學院 (論文 0059)

記憶體內運算 (CIM) 已成為傳統數位實作極具吸引力的替代方案,適用於廣泛的乘法和累加 (MAC) 作業,適用於深度神經網路 (DNN) 應用。喬治亞理工學院展示了 RRAM 技術的無 ADC 記憶體內運算 (CIM) 巨集,此巨集由 1T1R 位元單元組成。多數 CIM 巨集採用 ADC,其會因為量化和雜訊而造成效能限制和準確度下降。這項技術提出了使用類比訊號處理和直接數位化的無 ADC 記憶體方案,可將感測電路的佔用面積減少 0.5 倍,並將處理量提高 6.9 倍。提案的方案亦達到 11.6 倍的能效提升和 4.3 倍的運算效率提升。

Fig. 3. Structure and operation of the proposed ADC-free compute scheme using 1T1R array.

圖 3. 提案的使用 1T1R 陣列的無 ADC 運算方案的結構和作業。

圖檔:1421

標題:(左)提案的使用 1T1R 陣列的無 ADC 運算方案的結構和作業。(右) 帶有指示子區塊的標籤的雙陣列 RRAM 巨集的晶片照片。

## 技術焦點

#### 進階 CMOS 技術

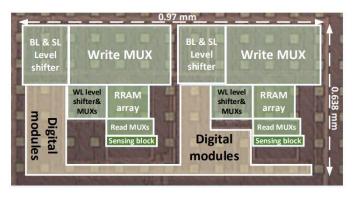

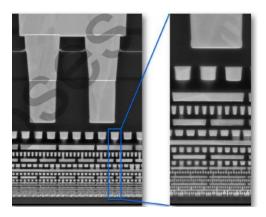

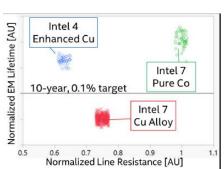

「Intel 4 CMOS 技術採用先進的 FinFET 電晶體,針對高密度和高效運算進行了最佳 化」- Intel (論文 1787)

摩爾定律持續快速發展:Intel 推出全新的先進 CMOS FinFET 技術,即 Intel 4,此技術提供 2 倍的高效能邏輯庫面積縮放和比 Intel 7 高出 20% 的等功率效能,持續擴展摩爾定律。縮放 後的高效能庫提供 50nm 閘極間距、30nm 鰭片間距和 30nm 最小金屬間距。此節點為 N/PMOS 提供 8VT (4NVT + 4PVT),範圍為 190mV/180mV,讓設計人員能在功率和速度需求之間進行選擇。EUV 光刻技術廣泛用於簡化製程及提高良率。互連堆疊有 16 個金屬層,在 關鍵的較低層採用強化的銅冶金,以提供更優異的電遷移和更低的線阻。

圖檔:1787

圖 1 標題:Intel 4 互連堆疊的橫截面視圖。EUV 圖案用於較低的金屬層,以簡化製程並提高 產量。

圖 2 標題:比較 Intel 4 與 Intel 7 技術之間不同冶金學的歸一化電遷移壽命與歸一化線阻。

#### 進階 CMOS 技術

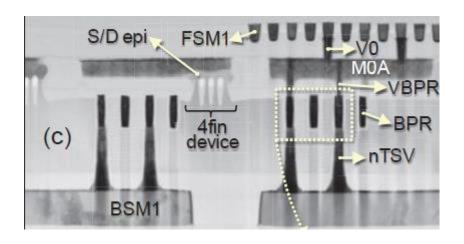

「使用晶圓兩面透過埋入式電源軌進行路由連接的可微縮式 FinFET」— imec (1419)

近年來,imec 開發出埋入式電源軌 (BPR) 技術,將電源軌推到電晶體下方,具有降低 IR 壓降和提高佈線密度的雙重好處,訊號路由和電源路由從此不再有佈線衝突。imec 在此回報了具有新穎路由方案的微縮式 finFET,此方案可透過 BPR 從晶圓兩面進行電源連接。在經過最佳化的預清潔,同時保持良好的接觸介面的單一金屬化步驟中,執行通孔圖案化後的正面與p/n S/D-epi 和 BPR 的接觸。在晶圓翻轉、鍵合和極薄化之後,高度微縮的 323nm 深奈米矽通孔 (nTSV) 落在 BPR 上,可達到緊密的覆蓋控制和不變的 BPR 電阻。藉由將供電網路移至背面,提供更少的動態和靜態 IR 壓降,動態和靜態 IR 壓降是根據 2nm 設計規則為低功耗 64位元 CPU 產生的晶片內建功率熱圖所預測。P/NMOS 在背面處理和額外退火後顯示出相似或甚至更出色的 ION-IOFF,以改善 VT 恢復、遷移率和 BTI。

標題:TEM 影像展示採用創新佈線方案建構的 finFET,其中晶圓的兩面都用於透過埋入式電源軌 (BPR) 進行設備連接。高達 M1 等級的 FinFET 建構在晶圓的正面 (FS),然後將晶圓翻轉、鍵合到載體晶圓並薄化。在晶圓的 FS上, M1 線 (FSM1) 透過 V0 過孔連接到 M0A 線,然後透過 VBPR 過孔連接到 BPR 線。

## MRAM 記憶體技術

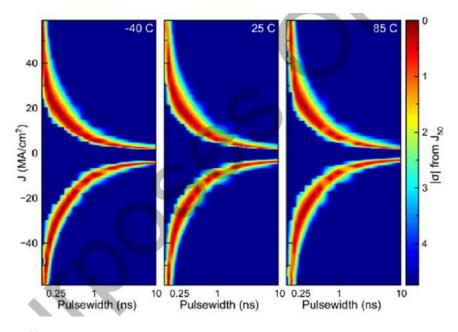

「具有雙自旋扭矩磁隧道結的可靠次奈秒 MRAM」- IBM (論文 1367)

自旋扭矩轉移磁阻隨機存取記憶體 (STT-MRAM) 技術已展現出比快閃記憶體或 SRAM 更出色的能量表現,且目前已進入量產階段。然而,STT-MRAM 位元單元裝置的可靠性和速度仍然是需要改進的因素。在本論文中,IBM 使用雙自旋扭矩磁隧道結 (DS-MTJ),在兩端子 STT-MRAM 裝置中展示次奈秒切換的兩大強化功能。透過 ≤250 ps 的寫入脈衝和在 -40°C 至85°C 的溫度範圍內的緊密分佈,可減少寫入作業發生的錯誤。為了建立可靠性,在 1E10 次寫入循環後沒有觀察到效能下降。將此兩端子 DS-MTJ STT-MRAM 裝置與最近發佈的三端子自旋軌道扭矩 (SOT) MRAM 裝置進行比較,顯示切換電流密度降低 10 倍,同類功耗降低 3至 10 倍。

標題:單一裝置的寫入錯誤率,使用正常的分位數標度 (使用與 50% 切換電流密度的標準偏差的絕對值) 繪製,在 -40 C、25 C 和 85 C 下測量,脈衝寬度為 225 ps 至 10 ns。

## DRAM 記憶體技術

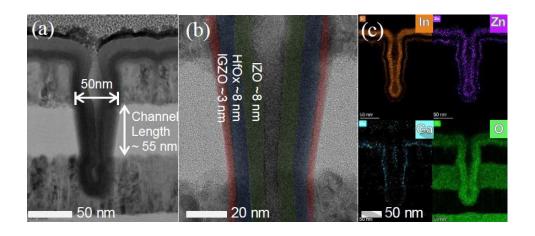

「垂直通道全面 (CAA) IGZO FET 小於 50nm CD, 具有 32.8µA/µm (Vth + 1V) 的高 讀取電流,在高達 120℃ 的溫度下具有出色的熱穩定性,適用於低延遲、高密度的 2T0C 3D DRAM 應用」– Huawei (論文 1736)

Huawei 首次回報高效能 DRAM 的發展情況,展示了一款垂直通道全面 (CAA) IGZO FET,縮小到小於  $50 \times 50 \text{nm}^2$  的主動面積。靠著最佳化的 IGZO 厚度 (~3nm) 和高 K 電介質 (HfOx),在通道長度 55 nm 和臨界尺寸 (CD) 50 nm 的 IGZO CAA FET 中,於 Vth +1V 時可達到  $32.8 \mu \text{A}/\mu \text{m}$  的高電流密度和 92 mV/dec 的次閾值擺幅。經過溫度變化測試和從 -40 °C 到 120 °C 的正偏壓溫度應力 (PBTS) 也證明其擁有良好的熱穩定性和可靠性。研究結果顯示,CAA IGZO FET 是未來  $1\alpha$  節點以上、高密度、高效能 3D DRAM 相當有前景的選擇。

標題:Huawei 的 IGZO-CAA (垂直通道全面) FET 横截面,TEM 測得的 CD 約為 50nm。8nm

HfOx 電介質加上 55nm 通道長度 (大約值)

## PCM 記憶體技術

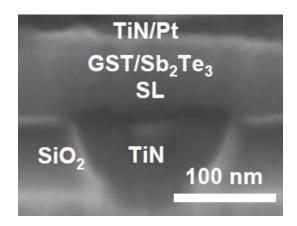

「首次展示基於 Ge2Sb2Te5 的超晶格相變記憶體,具有低復位電流密度 (~3 MA/cm2) 和低電阻漂移 (~0.002,在 105℃ 下)」- 史丹佛大學 (論文 1387)

相變記憶體 (PCM) 能為需要高密度儲存的各種應用提供可編程和非揮發性記憶體。史丹佛大學展示 PCM 記憶體結構的進展,研究了降低復位電流密度 (Jreset) 和電阻漂移係數 (v) 的超晶格 PCM (SL-PCM) 異質結構。然而,SL 尚未搭配眾所周知的相變材料 Ge2Sb2Te5 (GST) 進行研究,SL 介面與混合層的影響仍屬未知。此處首次使用基於 GST/Sb2Te3 的 SL,其在蘑菇細胞 PCM 中同時實現 Jreset  $\approx$  3-4 MA/cm² 和 7 個電阻狀態 (v  $\approx$  0.002),底部電極直徑最低至 110nm。即使分別經過 106 次循環和高溫 (105°C) 後,低 Jreset 和 v 也保持不變。團隊還發現,SL-PCM 中的 Jreset 和 v 都隨著 SL 介面數量的增加而減少。

圖檔:1387

標題:蘑菇細胞 GST/Sb2Te3 超晶格相變記憶體裝置的電子顯微鏡圖像橫截面掃描,插圖顯示原子級解析度的超晶格介面和類范德華間隙。

#### 影像感測器技術

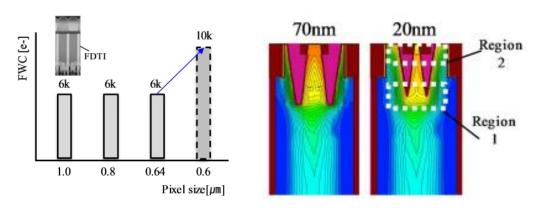

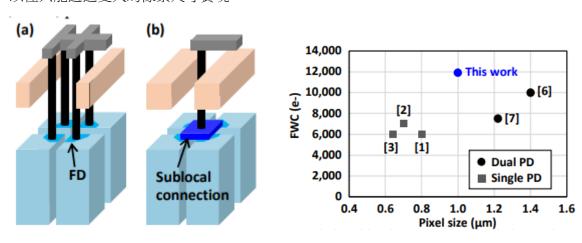

「採用雙垂直傳輸閘技術、全井容量 10,000e-、0.6µm 小像素的高解析度 CMOS 影像感測器」— Samsung (論文 1704)

CMOS 像素競賽仍在進行中: Samsung 使用雙垂直傳輸閘 (D-VTG) 技術開發了一款 0.6μm 像素,全井容量 (FWC) 10,000e-的 200Mp 影像感測器原型。D-VTG 的 FWC 比單垂直傳輸閘 (S-VTG) 增加了 60%,並透過提高 TG 電壓的可控性來提高傳輸能力。亦透過 VTG 的間隙、深度和錐度斜率,達到最佳化的光電子傳輸。

圖檔:1704

圖 1 標題: Samsung 的全井容量會依像素大小而有所不同。在 0.6um 間距像素下,全井可達

到 10ke-。

圖 2 標題:單垂直傳輸閘和雙垂直傳輸閘的電位分佈

## 有線和光學系統

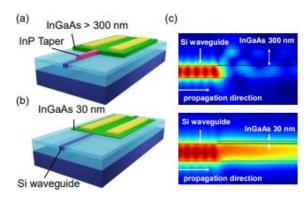

「針對無接收器系統的 Si 槽波導上的低電容超薄 InGaAs 薄膜光電探測器」 - 東京大學 (論文 1455)

東京大學提出一款由超薄 InGaAs 薄膜和 Si 槽波導組成的 Si/III-V 混合波導光電探測器,可實現低電容和高回應度,同時提高高速資料中心和骨幹鏈路的速度。Si 槽波導中的強光限制增強了 InGaAs 薄膜中的光吸收。結果,研究團隊成功地展示了 1A/W 的高回應度和相當低的 1.9fF 小電容,實現無接收器 (TIA-less) 系統。

圖檔:1455

標題: (a) 具有錐度的傳統 InGaAs 波導光電探測器和 (b) 提案的超薄 InGaAs 薄膜波導光電探測器的示意圖。超薄 InGaAs 薄膜波導光電探測器更平滑的模式轉換和低反射可以消除 InP錐度,實現更簡單的製程。(c) 從 Si 波導到光電探測器的模式傳播。使用超薄 InGaAs 薄膜,可實現平滑模式轉換,消除錐度。

#### 有線和光學系統

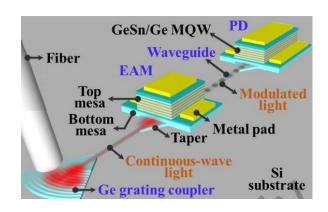

「用於 2μm 波長光電積體電路的 300mm Si 基板首次單片整合 IV 族波導光電探測器 和調變器 <sub>1</sub> – 新加坡大學 (論文 1676)

面對 1310 和 1550nm 單模光纖的發展已逼近理論極限,靠著一條路徑中的 2μm 光譜窗口將可解決通訊容量緊縮問題。新加坡大學回報第一次在支援 Si CMOS 量產路線、用於 2μm 波長應用的 300mm Si 基板上單片整合 IV 族波導光電探測器 (PD) 和調變器。儀器的波導 PD 和電吸收調變器 (EAM) 採用 Ge0.92Sn0.08/Ge 多重量子井 (MQW) 作為有源層。利用 Ge 緩衝層作為 Ge-on-Si 波導和光柵耦合器,以便將光分別耦合到 EAM 和 PD,以進行直接調變和偵測。其波導 PD 中的擴展耦合路徑使光學回應度比具有相同吸收層的表面照明模式高 35倍,在所有高 3dB 頻寬 6GHz 基於 GeSn 的 2μm PD 中具有最高的 525mA/W 回應度。此外,團隊首次展示了 2μm 全整合式收發器的可行性,並在同一 Si 基板上成功操作 PD 和 EAM。

圖檔:1676

圖 1 標題:Si 基底上 2  $\mu$ m 波長的單片整合式波導 PD 和 EAM 的 3D 示意圖。光通過耦合器耦合到波導並傳輸到 EAM 進行調變,然後由 PD 偵測

圖 2 標題: 2 μm 整合式平台 300 mm Si 基底上 GeSn MQW 層堆疊的橫截面 TEM 影像。

## 先進材料

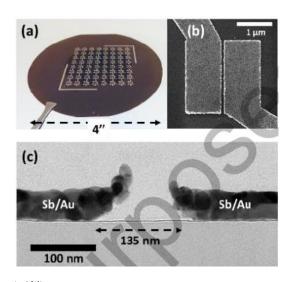

「晶圓級 Bi 輔助半自動乾式轉移及製造高效能單層 CVD WS2 電晶體」— TSMC (論文 1500)。

TSMC 報告了一種電晶體技術,此技術採用一種創新的晶圓級半自動乾式轉移製程,用於利用半金屬 Bi (鉍) 和二維半導體 WS₂ 之間的弱耦合介面開發出的單層 (1L) CVD WS₂。單層 2D 半導體已展現出可作為未來電晶體技術最終尺寸溝道材料的巨大潛力,因為其在原子級溝道厚度下可保持良好的載流子遷移率,且在更短的溝道長度 (LCH < 10nm) 下比大型半導體具有更好的靜電控制。這種新的單層轉移方法進行了晶圓級的示範。此製程中的 n-FET 在  $V_{DS}$  = 1V、接觸電阻 <0.73k $\Omega$ · $\mu$ m 和 135nm 閘極長度時可達最高 250 $\mu$ A/ $\mu$ m 的高導通電流。

圖檔:1500

標題: (a) 2" 1L CVD WS2 轉移至具有全域背閘裝置結構的 4" SiNx (100 nm)/p++-Si 晶圓的

照片。(b) 具有 Sb/Au 接點的裝置結構的 SEM 和 (c) 橫截面 TEM 影像。

## 影像感測器技術

「用於大電位井容量和高量子效率的氧化基全溝槽隔離 2 層電晶體像素堆疊 CMOS 影像感測器」— Sony (論文 1102)

Sony 展示具有大電位井容量 (FWC) 和高量子效率 (QE) 的 2 層電晶體像素堆疊 CMOS 影像 感測器 (CIS) 的開發。光電二極體 (PD) 和像素電晶體透過三維順序整合製程在不同的 Si 層上製造,以增加 PD 體積,並導入連接多個浮動擴散的新子區域連接,改善轉換增益和隨機雜訊。首次使用氧化矽代替傳統的多晶矽作為全溝槽隔離 (FTI) 的嵌入材料,以防止光由 FTI 吸收,並將 530nm 波長的 QE 提高 19%。團隊展示了 FWC 12,000e- 的 1.0µm 雙 PD CIS,這以往只能透過更大的像素尺寸實現。

圖檔:1102

標題:(a) 不含和 (b) 含子區域連接的 2 層像素的裝置結構。(c) 與先前的研究相比,此技術中像素大小和 FWC 之間的關係。

## 電路焦點

## 機器學習

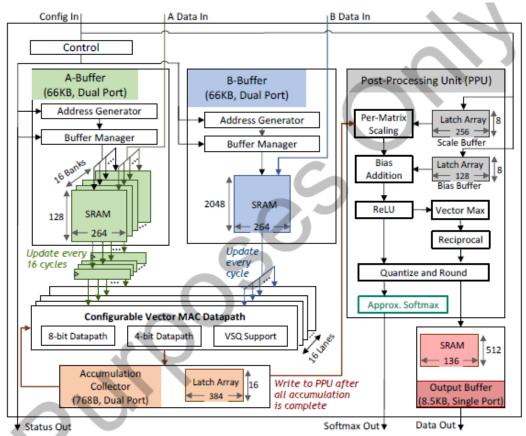

「用於 5nm 變壓器支援每向量縮放 4 位元量化的 17-95.6 TOPS/W 深度學習推理加速器」– NVIDIA (論文 1271)

用於自然語言處理或機器視覺的專屬機器學習處理器,正在成為邊緣裝置和資料中心內的主力。NVIDIA的研究人員展示了其最新的 5nm CMOS 深度學習加速器原型。在加速器中,高精度運算和高功耗之間存在根本性的關聯。另一方面,低準確率的運算大多會導致錯誤分類,導致使用者不滿。作者提出一種全新方法來應對此挑戰,透過採用資料相關向量縮放來執行4b的算術任務,準確率損失只有 0.7%,產生 95.6 TOPS/W 的功率效率。

Fig.5: Accelerator block diagram.

圖檔:1271

標題: NVIDIA 提出支援每向量縮放量化的深度學習推理加速器的方塊圖

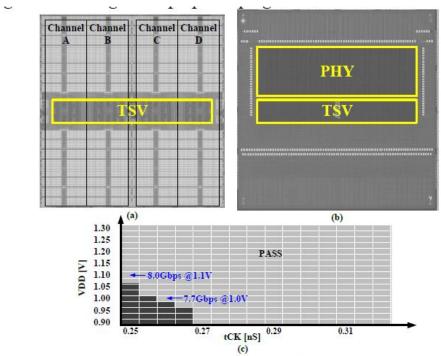

#### DRAM 記憶體

「具有用於增強 RAS 功能的晶片內建錯誤控制方案的 16GB 1024GB/s HBM3 DRAM」- Samsung Electronics (論文 1170)

Samsung 展示其第三代 10nm DRAM,其效能獲得改善,用於提高系統可靠性、可用性和可維護性 (RAS),適用於汽車、工業和資料中心等應用。Samsung 在「高頻寬記憶體 3」 (HBM3) DRAM 中實現了此一目標,透過專注於改善錯誤修正,採用新的晶片內建錯誤程式碼修正 (ECC) 方案,可同時修正 16 位元字詞錯誤和 2 個單位元錯誤。在同一 DRAM 晶粒上本機修正每個錯誤,無需存取 DRAM 堆疊中的其他晶粒,如此將可改善延遲並將引腳資料速率從上一代的 5Gb/s/pin 提高到 8.0Gb/s/pin,且每個記憶體立方體的總記憶體頻寬可達到 1024Gb/s。這透過 16GB DRAM 模組呈現。

Fig. 6. Chip microphotographs of (a) Core-die and (b) Buffer-die, (c) measured tCK shmoo.

Fig. 6. Chip microphotographs of (a) Coredie and (b) Buner-die, (c) measured tCK shmoo.

圖 6. (a) Core-die 和 (b) Buner-die 的晶片 顯微照片,(c) 測量的 tCK shmoo。

圖檔:1170

標題: Samsung HBM3 的 (a) Core-die 和 (b) Buffer-die 晶片顯微照片, (c) 測量的 tCK shmoo。

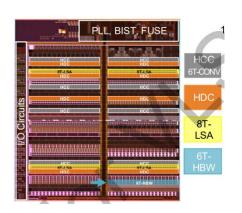

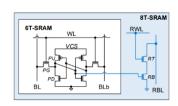

## SRAM 記憶體

「採用 Intel 4 CMOS 技術的節能高頻寬 6T SRAM 設計」 – Intel (論文 1664)

Intel 的作者展示了採用 Intel 4nm 級 CMOS 技術的節能 SRAM。針對高處理量應用的節能運算需求,為晶片內建記憶體帶來更高容量和頻寬的挑戰。傳統的 6T SRAM 可符合低面積要求,而 8T 位元單元則擁有較低的動態功率,但這兩者都不能克服這些挑戰。本論文介紹一種最佳化的 6T SRAM 設計,其位元單元面積為 0.03µm²,功耗與 8T 相似,動態功耗比傳統 6T 設計降低 5.6 倍。

|                              | 8T-LSA<br>(8T-SRAM bitcell)             | 6T-CONV<br>(HCC bitcell)        | 6T-HBW<br>(HCC bitcell)         |

|------------------------------|-----------------------------------------|---------------------------------|---------------------------------|

| Array Efficiency,<br>Density | 52%,<br>13.7 <b>M</b> b/mm <sup>2</sup> | 75%,<br>23.8 Mb/mm <sup>2</sup> | 61%,<br>19.4 Mb/mm <sup>2</sup> |

| Overall Macro Area [1]       | 1.74 x                                  | 1 x                             | 1.23 x                          |

| Read Energy / access[1,2]    | 1 x                                     | 5.81 x                          | 1.03 x                          |

| Write Energy / access[1,2]   | 1 x                                     | 11.9 x                          | 1. <b>4</b> 7 x                 |

| Bitcell Leakage              | 6 x                                     | 1 x                             | 1 x                             |

11 Output muxes are excluded from area and energy calculations

22 Read and write energy measurements are based on 50% '0' and 50% '1' array data for both read and write

圖檔:1664

標題: (a) Intel 4 CMOS 技術測試晶片的晶粒顯微照片。(b) Intel

4 CMOS 技術記憶體位元單元。(c) 60kB 巨集實作每次存取的密度和能量比較

#### SRAM 記憶體

「能為 AR 應用降低 58% 記憶體功耗在 7nm SoC 中使用循序存取模式的協同最佳化 SRAM 電路」— Meta (論文 1148)

對 AR 應用來說,具備邊緣智慧的感測器需要達到超低功耗。在本文中, Meta Reality Labs 團隊說明嵌入在原型肌電圖 (EMG) 腕帶中用於 AR 眼鏡手勢辨識任務的 7nm SOC 中 SRAM 的低功耗設計。團隊提出特定的循序操作,而非使用隨機存取,用於針對感測模式最佳化的記憶體設計,這類設計中的電路已將連續記憶體讀寫作業次數降到最低。與傳統記憶體設計基準相比,此設計的讀取功耗降低 52%,寫入功耗降低 58%。

Fig. 1: (a) Application analysis of AR SoC SRAM data access showing high sequentiality. (b) Chip die photo and demo setup. Measured energy at  $124 \,\mu\text{J}$  per 'pinch-and-release' hand gesture detection.

Fig. 1: (a) Application analysis of AR SoC SRAM data access showing high sequentiality. (b) Chip die photo and demo setup. Measured energy at 124µJ per 'pinch-and-release' hand gesture detection.

圖 1: (a) 顯示高循序性的 AR SoC SRAM 資料存取的應用分析。(b) 晶片晶粒照片和展示設定。每次「捏放」手勢偵測的測得能量為  $124\mu J$ 。

圖檔:1664

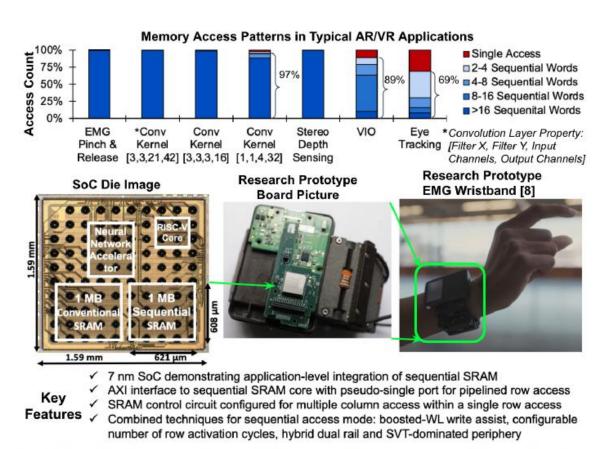

#### 系統級封裝電源管理

「具有自修整、數位控制導通時間不連續導通模式 (DCM) 作業,採用 22nm CMOS 有源矽中介層,用於異構 3D-TSV 堆疊系統級封裝,含封裝嵌入式電感器的全整合穩 壓器」– Intel (論文 1117)

Intel 報告其先進的系統級封裝 (SiP) 電源管理,在 22nm 有源矽中介層上整合異構小晶片與 3D-TSV 堆疊系統級封裝 (SiP) 設計。作者將電感器嵌入封裝基板中,與 3D-TSV 直接連接,以區塊形式直接連接到中介層晶粒內建的全整合穩壓器。單一區塊的電源效率在 10mA – 300mA 範圍內保持平穩,透過在相鄰區塊內建選擇性組合的穩壓器以實現高達 1A 的功率效率。為具有不同功率要求的各種運算、記憶體和通訊小晶片提供彈性且具有成本效益的整合。

Figure 2: 10-tile test setup with inductor specifications

圖 2: 具有電感器規格的 10 區塊測試設定

圖檔:1117

標題:Intel 的 10 區塊全整合 DCM 電壓調節器測試設定,內含各種 TSV 技術電感器,可針對功率/效率/面積做選擇

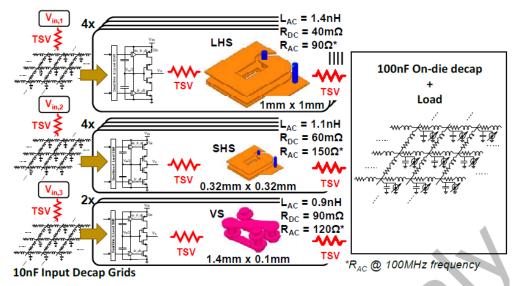

### 數位處理器的電源管理

「用於動態電壓縮放行動應用具有高電流密度的 3nm GAAFET 類比輔助數位 LDO」 – Samsung 電子 (論文 1336)

具有許多處理核心的先進 CMOS 節點中的行動式 SoC 的運算需求正不斷提高,進而增加電源管理上的挑戰。Samsung 的作者展示其類比輔助數位 LDO 解決方案,該解決方案採用 3nm 閘極環繞 FET (GAAFET) 技術,提供高電流密度功率的傳輸。此設計具有主動電源雜訊消除和 CPU 核心的快速瞬態負載偵測功能。其混合式 LDO 設計可在 <1mA 至 1.4A 負載範圍內實現精確調節,1ns 內 1A 動態負載的電源壓降僅 38mV。

Fig. 3. Proposed hybrid LDO structure with high current density

Fig. 3. Proposed hybrid LDO structure with high current density

圖 3. 所提出具有高電流密度的混合式 LDO 結構

圖檔:1336

標題: Samsung 提出用於行動式 SoC 應用的混合式 LDO 結構。

#### 有線收發器

「適用於 200+Gb/s 序列連結採用 4nm FinFET CMOS,72GS/s、8 位元 DAC 的有 線發送器」– IBM Research,美國 (論文 1241)

IBM 報告了一種用於超高速序列電氣連結的發射器,可滿足資料中心不斷增加的網路頻寬的需求。其方法是採用具有 72GS/s 作業和來源串聯終端 (SST) 拓撲的 8 位元 DAC。先前採用 SST 設計的作品從未超過 56GBaud,而這項作品提高到了 72GBaud。團隊的 4nm FinFET CMOS IC 展示了 216Gb/s PAM8 和 212Gb/s QAM64 OFDM 作業,功耗為 288mW。

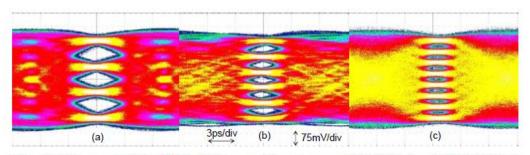

Fig. 8 Measured 72GS/s TX eye diagrams w/ FFE8 for (a) 144Gb/s PAM4 QPRBS13 (b) 180Gb/s PAM6 PRBS11 (d) 216Gb/s PAM8 PRBS15

Fig. 8 Measured 72GS/s TX eye diagrams w/ FFE8 for (a) 144Gb/s PAM4 QPRBS13 (b) 180Gb/s PAM6 PRBS11 (d) 216Gb/s PAM8 PRBS15

圖 8 (a) 144Gb/s PAM4 QPRBS13 (b) 180Gb/s PAM6 PRBS11 (d) 216Gb/s PAM8 PRBS15 測得的 72GS/s TX 眼圖及 FFE8

圖檔:1241

標題:(a) 144Gb/s PAM4 (b) 180Gb/s PAM6 和 (c) 216Gb/s PAM8 的 IBM 所測得 72GS/s

TX 眼圖及 FFE8

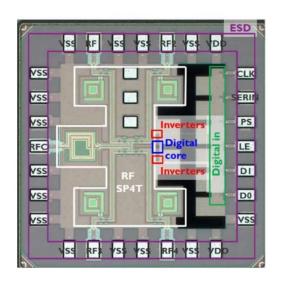

#### 5G 收發器

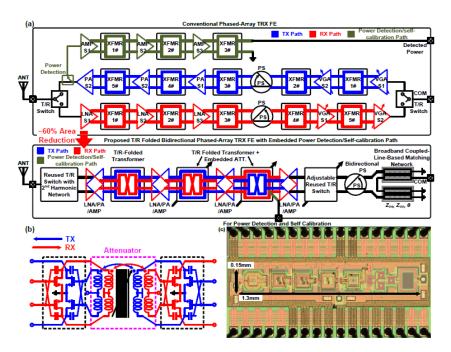

「適用於 65nm CMOS 技術的 5G 支援 28/39GHz 頻段的 64/256/512QAM 具有嵌入式 TX 功率偵測/自校正路徑的超輕巧型雙向 T/R 折疊式 25.8-39.2GHz 相控陣收發器 前端」- 清華大學 (論文 1802)

清華大學的研究人員展示了一種極具面積效率的 5G 雙向發射器和接收器,可在 28-39GHz 的寬頻率範圍內相容,以相容全球採用的不同頻段。採用頻寬變壓器的發射器和接收器導入快速切換、衰減和移相技術來實現頻寬波束成形。此作品支援 28-39GHz 的 64/256/512QAM,具有 19.2dB RX 增益和 >12.8dBm TX 功率。其面積比先前的技術減少 25% 以上。

標題: (a) 清華大學提出具有嵌入式功率偵測/自校正路徑的超輕巧型雙向 Tx/Rx 折疊式 28/39GHz 頻寬相控陣收發器前端。(b) 提出的 Tx/Rx 折疊架構,Tx/Rx 重複使用採用雙向變壓器的高解析度衰減器。(c) 晶粒顯微照片。

#### 5G 收發器

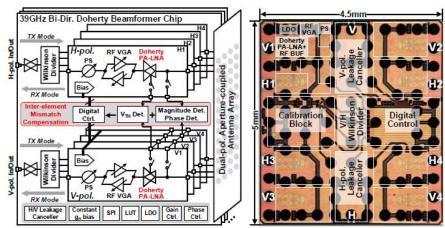

「使用 Shared-LUT DPD 和用於 5G 基地台的元件間誤差補償技術的 39GHz CMOS 雙向 Doherty 相控陣波束形成器」- 東京工業大學 (論文 1383)

東京工業大學報告了一款以相控陣波束形成器為基礎的 5G 收發器,此波束形成器採用 Doherty 低雜訊功率放大器。團隊研究了數位和類比校正領域的強化功能,提高單一天線上 TX 功率輸出的均勻性。他們所提出的方法對每個天線使用共用數位校正以及單獨的相位和增益校正,將發射誤差向量幅度 (EVM) 提高 9.1%,將發射到接收的 EVM 提高 11.8%。在 64 QAM 調變下每秒最多顯示 3.5G 符元,而且此晶片也支援 21-Gb/s 單載波資料流。

Fig. 1. Proposed phased-array beamformer chip and die micrograph.

Fig. 1. Proposed phased-array beamformer chip and die micrograph.

圖 1. 提出的相控陣波束形成器晶片和晶粒 顯微照片。

圖檔:1383

標題:東京工業大學的具有元件間誤差補償的 39-GHz 雙向 Doherty 相控陣波束形成器。

#### 成像和 LIDAR

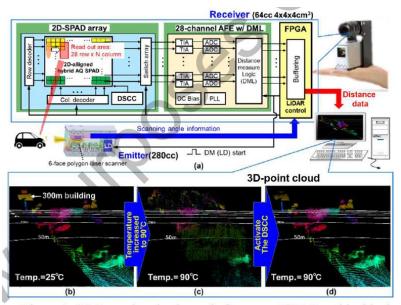

「帶有 HV/LV 電晶體混合主動重置 SPAD 陣列和背景數位 PT 補償的 1200x84 像素 30fps 64cc 固態 LiDAR RX」 – Toshiba (論文 1288)

LIDAR 近期因固態 VLSI 接收器和輕巧型發射器的推動而降低了尺寸與成本。Toshiba 展示了一款以 CMOS-SPAD 為基礎的 LIDAR 接收器,此接收器嵌入在手掌大小般 64cc 體積的系統內。1200x84 感測器嵌入了最佳化的主動重置 SPAD 像素,具有深溝槽隔離 (DTI)。SPAD 的高操作電壓會增加許多晶片外部元件的成本:此工作嵌入了一個晶片內數位背景低壓控制迴路,用於補償 SPAD 製程和溫度漂移,因此可減少系統材料清單。此 LIDAR 系統結合了CMOS 接收器與微型掃描鏡、28 通道 ADC 和 FPGA,在高達 90°C 的系統溫度下,於110kLux 的明亮環境光下以 30FPS 的速度在室外展示 3D 點雲的產生。

Figure 4. (a) Our palm-sized proof of concept LiDAR and its block diagram. (b) The 3D point cloud data at 25°C and (c) at 90°C with the proposed DSCC OFF, and (d) DSCC ON.

Figure 4. (a) Our palm-sized proof of concept LiDAR and its block diagram. (b) The 3D point cloud data at 25°C and (c) at 90°C with the proposed DSCC OFF, and (d) DSCC ON.

圖 4 (a) 手掌大小的概念驗證 LiDAR 及其 方塊圖。(b) 25°C 時的 3D 點雲資料,和(c) 90°C 且關閉提議的 DSCC 時,和(d) 開啟 DSCC 時。

圖檔:1288

標題: (a) Toshiba 手掌大小的概念驗證 LiDAR 及其方塊圖。(b) 25°C 時的 3D 點雲資料,和(c) 90°C 且關閉提議的 DSCC 時,和 (d) 開啟 DSCC 時。

#### 成像和 LIDAR

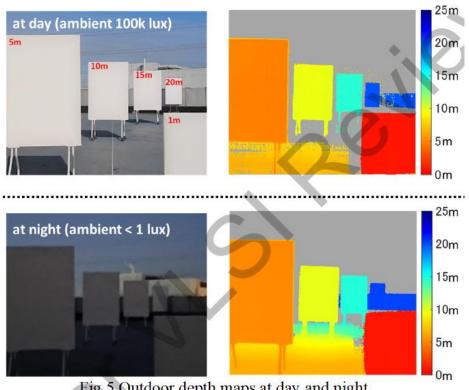

「用於在高環境光條件下進行遠距 3D 景深測量的混合間接 ToF 影像感測器」— Toppan Inc. (論文 1190)

用於 3D 景深相機和 LIDAR 的高解析度間接飛行時間 (ToF) 影像感測器,通常需要在距離範圍或精度之間做取捨。Toppan Inc. 與 Brookman Technology 和靜岡大學的研究人員合作,提出一種用於間接 ToF 的新時序方案,能同時實現長距離和高精度,無須再取捨。此感測器技術適用於包括戶外用途在內的廣泛應用,研究團隊提出了一種干擾抑制技術,允許多部攝影機同時在同一視場中工作。他們展示了 VGA 感測器中的技術,可實現 30m 範圍的成像,同時在高達 100Lux 的環境光下保持 <15cm 的精度。

Fig. 5 Outdoor depth maps at day and night.

| Fig. 5 | Outdoor depth maps at day and |

|--------|-------------------------------|

| night. |                               |

圖 5 白天和晚上的戶外景深圖。

圖檔:1288

標題: Toppan Inc 的混合 TOF: 白天 (100k lux) 和晚上 (< 1 lux) 範圍內 1-20 m 的室外景深 昌。

## 類比轉數位轉換器

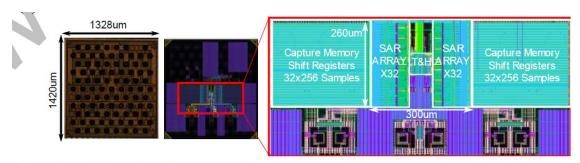

「採用 4nm CMOS 具有自舉採樣器和 AB 類緩衝器的 8 位元 56GS/s 64x 時間交錯式 ADC / - IBM Research , 瑞士 (論文 1215)

瑞士 IBM Research 報告了採用先進 4nm CMOS 的 56GS/s ADC, 其解析度為 8b。用於高 速序列連結的現代化 ADC 型接收器需依靠時間交錯方法,以達到 112Gb/s 以上的所需速度。 此技術將 64 個 ADC 通道與用於通道間偏移、增益和偏斜校正的類比前景校正交錯。有一款 新穎的 AB 類輸入緩衝器和自舉追蹤與保持採樣器,不需要高供應電壓,可在與 4nm 技術節 點相容的 0.8V 單一低供應電壓下作業,且仍能維持在 0.8V 的峰對峰輸入擺幅。此設計在超 過 27GHz 頻寬下以 47fF/轉換步能效實現符合最先進技術水準的效能。

Fig. 5 ADC die micrograph and layout details.

| Fig. 5 ADC die micrograph and layout | 圖 5 | ADC 晶粒顯微照片和佈局細節。 |

|--------------------------------------|-----|------------------|

| details.                             |     |                  |

標題:IBM 採用 4nm CMOS 技術製造的 56 GS/s 8 位元異步 SAR ADC 的晶粒顯微照片和佈局細節。16x4 交錯式 ADC 在第一級交錯器中使用創新的自舉技術和 AB 類跟隨器。