# 2023 年度 VLSI 技术与电路研讨会的技术要点

2023年 VLSI 技术与电路研讨会是记录微/纳米集成电子的发展速度、进展和演变的顶级国际会议,定于 2023年 6月 11日至 16日举行。该研讨会将在日本京都丽嘉皇家酒店以线下方式举行,以增加交流的机会。

研讨会的总体主题"**重启技术和电路,实现可持续未来**"旨在将先进的技术开发、创新的电路设计及其所能实现的应用整合在一起,努力促进全球社会向智能互联设备、基础设施和系统所代表的新时代过渡,从而改变人类相互交流的方式。

以下是针对此主题的一些重点论文:

# 技术与电路联合研讨会亮点

以下是一些联合重点论文,旨在推动技术和电路领域的共同进步:

#### 处理器

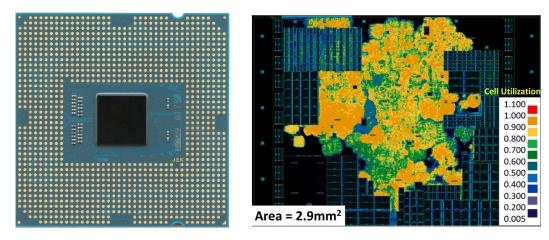

"采用PowerVia(背面电源)技术的英特尔4的E核实现"——英特尔公司(论文T1-1)

英特尔报告了一项高收益背面供电技术(PowerVia 技术\*)及采用 PowerVia 技术的英特尔 E核实现。PowerVia 技术是一项突破性的创新,它扩展了摩尔定律的缩放范围,使核心大面积的标准单元利用率超过 90%,同时由于 IR 压降减少,硅的频率提升超过 5%。在吞吐时间略高但可接受的情况下,硅后调试演示成功。PowerVia 测试芯片的热特性符合逻辑扩展所应有的更高功率密度。

\*会议 T6-1 对 PowerVia 技术进行了介绍。

图: (左) 采用 PowerVia 的英特尔 4 的芯片图。(右) 电池密度图。

# 用于机器学习的器件和加速器

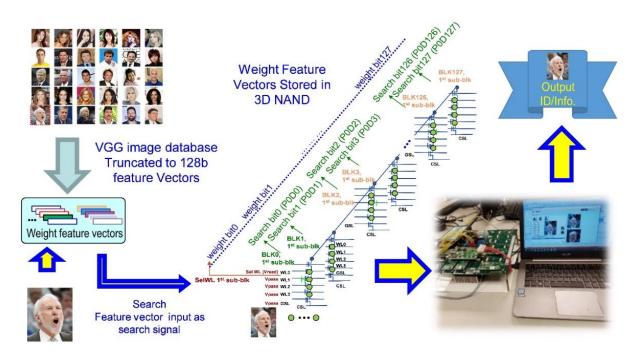

"用于三态内容可寻址存储器(TCAM)和汉明距离邻近搜索、基于3DNAND的高密度(43Gb)和高搜索带宽(300Gb/s)存內搜索加速器的芯片演示"——Macronix International Co., Ltd.(论文T15-1)

Macronix 展示了基于 96 层 3D NAND 产品的高密度(43Gb)存内搜索芯片。新型字符串选择 线路设计实现了 300Gb/s 的搜索带宽,测量功率小于 400mW,同时加快了精确的 TCAM 和汉 明距离邻近搜索。

图: IMS 操作的处理流程。它们使用公共人脸识别(VGGGace2 数据库)进行演示。特征向量(在本例中为 128b)被提取并存储在芯片中。对于数据查询,将搜索数据输入到芯片中,芯片可以直接计算出哪个 BL 地址与结果匹配。

# 技术亮点

# 先进 CMOS 技术

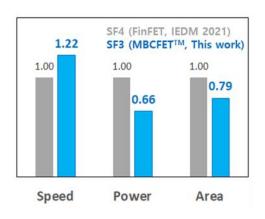

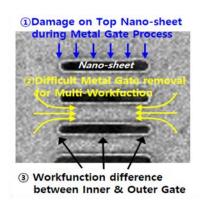

"全球首款采用新型多桥通道场效应晶体管(MBCFET)工艺的GAA 3nm 晶圆代工平台 技术(SF3)"——三星电子有限公司(论文T1-2)

本文报告了备受期待的从鳍式场效应晶体管向全环绕栅极(GAA)晶体管架构过渡的技术细节。三星发布了全球首款 GAA 3nm 代工平台技术 SF3,与 4nm 鳍式场效应晶体管平台相比,该技术的速度提高了 22%,功耗降低了 34%,逻辑面积减少了 0.79 倍。SF3 技术是业界首款量产 GAA(SF3E)的升级版。SF3 通过多桥通道场效应管(MBCFET™)独特的工艺设计,在标准单元高度固定的情况下提供各种纳米片宽度,性能相当优越,可显著增强鳍式场效应晶体管平台上的芯片级功率-性能矩阵。

图: (左)旧式 4nm 鳍式场效应晶体管(SF4)与全球首款 3nm SF3 GAA(MBCFET™)的性能/功耗/面积(PPA)比较。(右)MBCFET™的横截面突出了独特的工艺优化。

# 先进 CMOS 技术

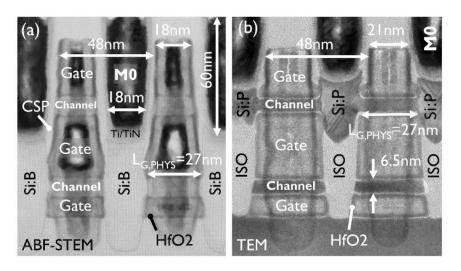

"基于纳米片的互补场效应晶体管(CFET)提供48nm 栅极间距和中间介电隔离,可实现 CFET 内部间隔层的形成和多 Vt 图案化"——imec(论文T1-3)

IMEC 的研究人员报告了行业相关栅极间距为 48nm 的硅纳米片单片互补场效应晶体管 (CFET),对底部或顶部器件都形成源极/漏极 (SD)和 SD 接触。成功展示了 30nm 垂直 N-P 空间下的 SD 外延图案化和高纵横比 SD 接触的形成。单片 CFET 具有良好的亚阈值摆幅,NFET 为 70mV/dec.,PFET 为 75mV/dec.。介绍了通过 SiGe 置换工艺形成的中间介电隔离 (MDI)是单片 CFET 内部间隔层形成和多  $V_T$ 图案化的推动因素。

图: (a) 底部 pFET 和 (b) 顶部 nFET 的横截面图。

# 先进工艺和材料

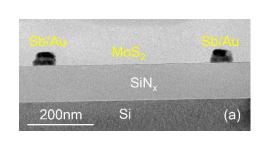

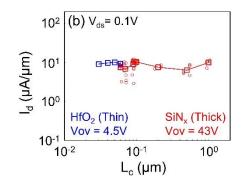

"缩放接触长度的单层 2D 通道晶体管具有低接触电阻"——台湾半导体制造公司、台湾阳明交通大学、南京大学、台湾成功大学(论文 T1-4)

由台积电领导的一项合作研究展示了  $Sb-MoS_2$  系统各缩放接触长度下低接触电阻的场景。这是使用二维过渡金属硫族化合物(2D TMD)实现超微缩逻辑晶体管的关键推动因素。2D TMD 有望实现超微缩的逻辑晶体管,而且这种巨幅的微缩还需要缩放接触长度。实验数据验证了所提出的 TCAD 模型,在接触长度小至 15 nm 时可以推测出 250 W-mm 的良好窄隙  $R_c$ 。

图: 触点的透射电子显微镜(TEM)图像(a)和宽 L。范围内的导通电流密度图像。

# 先进工艺和材料

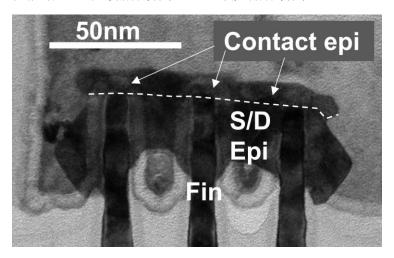

"非平面 FET 中低于 10° ohms.cm² 接触电阻率的接触腔整形和选择性 SiGe:B 低温外延工艺解决方案"——应用材料公司、IBM 半导体技术研究(论文 T1-5)

应用材料公司和 IBM 合作开发了一种接触腔整形工艺,允许活性硼掺杂水平达到  $2x10^{21}$  个原子/cm³。双方共同优化了 300mm 晶圆接触模块中的反应离子蚀刻(RIE)和选择性高掺杂

SiGe:B 外延工艺, 演示了历史最低的 11ohm.mm 晶体管接触电阻, 实现了器件的有效导通电流性能增益:中等晶体管为 44%, 领先晶体管为 19%。

图:鳍式场效应晶体管器件沿接触沟道的 TEM 横截面,显示出接触外延层的连续增长。

# 先进工艺和材料

超过 10um 深度的超高速蚀刻工艺使 400 层以上 3D NAND 闪存的存储通道孔的碳足迹 降低了84%。——Tokyo Electron Miyagi Ltd. (论文T3-2)

Tokyo Electron Miyagi 的作者开发了一种新颖的蚀刻工艺用于 3D NAND 闪存设备的高角度孔图案化,它采用了低温和新型无碳化学工艺。该技术的蚀刻深度达到 10mm,加工时间相当短(33分钟),可减少 84%的温室气体碳足迹,同时获得出众的蚀刻轮廓。

图:用新型化学低温工艺蚀刻后 ON 存储通道孔图案的横截面 SEM。

# 存储技术

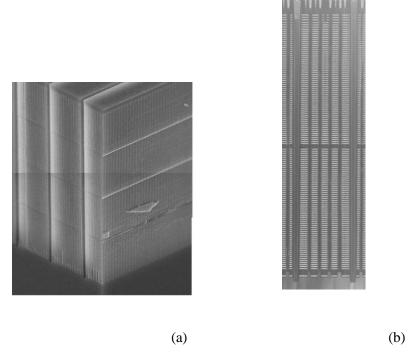

"用于超高(>300层)3D闪存垂直硅通道的高度可扩展金属诱导横向结晶(MILC)技术"——铠侠公司、西部数据公司(论文T7-1)

铠侠和西部数据展示了用于制造>300 层超高 3D 闪存的金属诱导横向结晶(MILC)技术。垂直存储孔中的 14μm 长空心硅(Si)通道通过 MILC 完全单晶化。通过使用新开发的吸镍技术,112 字线分层的 3D 闪存具有>40%的读取降噪性能和 10 倍的通道电导,而不会降低单元的可靠性。

图: (a) 超过 300WL 和 (b) 112WL 的 3D 闪存 TEM 图像

#### 存储技术

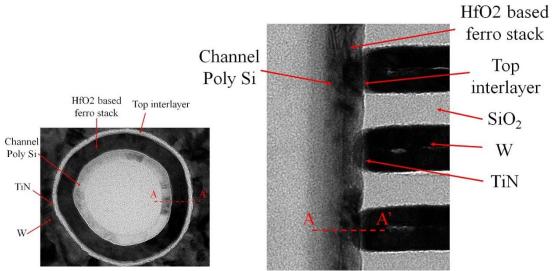

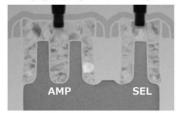

"QLC 可编程 3D 铁电 NAND 闪存使用存储单元堆栈工程进行存储窗口扩展"——SK Hynix Inc. (论文T7-2)

SK Hynix 首次展示了在量产中使用 3D 电荷陷阱氮化物(CTN)NAND测试车的 3D 铁电 NAND (Fe-NAND)四台阶存储单元(QLC)操作。他们优化了单元堆栈结构以改善存储窗口

(MW)。经优化的顶部中间层实现了四台阶存储单元(QLC),最小 Vth 间隙裕量为 0.24V。QLC 可编程 3D 铁电 NAND 闪存可实现高达 10.5V 的 PE 窗口扩展。

图:制造的 3D Fe-NAND的(a)平面图和(b)横截面 TEM 图像。

# 先进工艺和材料

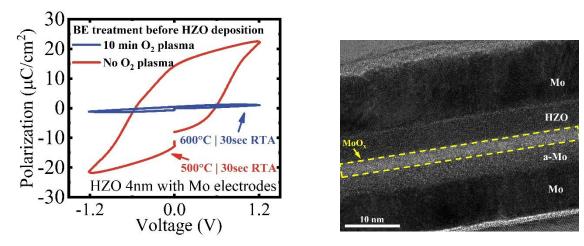

"首次观察到纳米级高性能铁电 HZO 钼电极电容器的超高极化(~ 108 mC/cm²)"——斯坦福大学、西部数据、内布拉斯加大学林肯分校、密苏里大学、SLAC 国家加速器实验室(论文T7-3)

由斯坦福大学领导的一项合作展示了厚 4nm、尺寸小于 100nm 的  $Hf_{0.5}Zr_{0.5}O_2$  (HZO)钼电极电容器的优异铁电性和耐久性。结果显示(1)400℃ 的低结晶温度;(2)1.2V 的低工作电压,> $10^{10}$  次耐久性循环;(3)通过添加  $CeO_2$  压力源降低唤醒效应和延迟疲劳;(4)通过精心设计的测量系统实现  $108mC/cm^2$  的极大铁电性。本文说明了整体材料/工艺工程的重要性以及  $HfO_2$  基铁电电容器特性改进的进一步潜力。

图: (左) 不同退火条件下氮化钛(TiN)和钼电极 HZO 电容器的铁电 P-V 曲线; (右) 制造的尺寸小于 100nm 的铁电电容器的自上而下图像。

#### 图像传感器技术

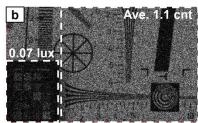

"采用非掺杂像素-鳍式场效应晶体管的 2 层晶体管像素堆叠 CMOS 图像传感器的噪声性能改进"——索尼半导体解决方案、索尼半导体制造公司(论文T7-4)

索尼首次提出了具有 2 个鳍的非掺杂像素-鳍式场效应晶体管的 2 层晶体管像素堆叠 CMOS 图像传感器。得益于非掺杂通道和更宽的通道鳍式场效应晶体管宽度,其跨导性能提高了 2.42 倍,随机噪声降低了 15%,随机电报信号减少了 99.3%。

#### (a) Fin (This work)

(b) Planar (Ref.)

图: (a) 像素-鳍式场效应晶体管通道和 (b) 2 层晶体管像素平面 FET 通道的横截面 TEM 图像。

### 超越 CMOS

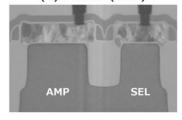

"用于大规模量子信号处理的基于 3D 可堆叠 InGaAs HEMT 的铌 (Nb) 超导体低温射频晶体管和布线电路"——韩国科学技术院、韩国基础科学研究所、庆北大学、韩国先进纳米技术制造中心(论文 T7-5)

韩国科学技术院的研究人员与韩国基础科学研究所、庆北大学和韩国先进纳米技术制造中心合作,报告了基于 3D 可堆叠 InGaAs HEMT、集成铌超导体的低温射频晶体管和布线电路。作者在 4K 分辨率下实现了创纪录的 601 GHz 高单位增益截止频率和 593 GHz 的单位功率增益截止频率,其功耗在所有已知低温射频晶体管中最小。此外,作者还展示了使用铌超导体和 III-V 异质结构混合互连的新颖结构,与传统结构相比,其布线电路的功耗降低了 41%。

图:基于 3D 堆叠 InGaAs HEMT 的(a) 双指低温射频晶体管和(b) 具有 III-V 异质结构本地 互连和铌超导体全局互连的低温 1 至 4 布线电路的假彩色 SEM 图像。

# 电路亮点

#### 处理器

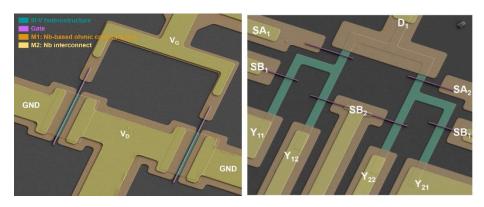

"用于端到端全时视觉的12nm 0.62-1.61 mW 超低功耗数字CIM 深度学习系统"——联发科(论文C3-4)

联发科的研究人员报告了数字存算一体(DCIM)可提供超低功耗深度学习系统,实现端到端全时视觉。作者提出了一个 SoC 原型,由基于 DCIM 的深度学习加速器(DCIM-DLA)、RISC-V 微处理器和片外图像传感器连接的接口组成。DCIM 支持混合精度计算,以平衡功耗和所需精度。该原型提供 51.2 GOPS 的峰值性能。此外,它还凭借 MobileNet-V1 上的人类检测混合精度实现了 57 TOPS/W 的能源效率和 85.7%的准确性。不带图像传感器的端到端系统的功率在 2 fps 和 15 fps 时分别为 0.62 mW 和 1.61 mW。

1.JTAG connection between host PC and debug access interface

2.Power supply

3.Main 12nm test chip

2.LED panel to show the result of detection

图: 展示的 SoC 原型由基于 DCIM 的深度学习加速器(DCIM-DLA)、RISC-V 微处理器和片外图像传感器连接的接口组成。不带图像传感器的端到端系统的功率在 2 fps 和 15 fps 时分别为  $0.62~\mathrm{mW}$  和  $1.61~\mathrm{mW}$ 。

# 图像传感器

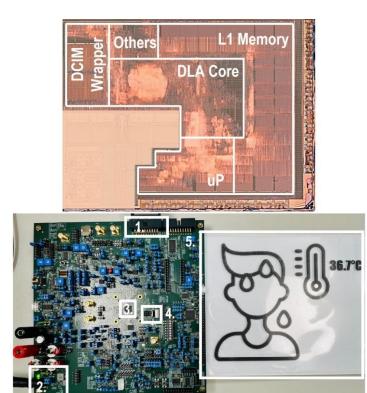

"采用集群多周期时钟充电技术、3.36mm 间距 SPAD 光子计数并具有中间最高有效位读数的图像传感器"——索尼半导体解决方案公司(论文C15-2)

使用 SPAD 像素的图像传感器即使在极暗的情况下也被寄望于能够捕获图像,这是因为它们通过捕获单个光子并直接计算其反应数来生成图像。另一方面,通过计算光子进入 SPAD 像素的反应数,增加了明亮场景中的电路尺寸和功耗。本文介绍了通过定期控制 SPAD 像素的复位来抑制明亮场景中的 SPAD 像素反应,从而降低功耗。通过将像素内计数器位减少到 8 位,像素大小也会压缩,因为上位数是通过计算像素内计数器的最高有效位(MSB)的变化次数来计算的。通过 22nm 节点工艺实现了 3.36mm² 的像素尺寸,是目前世界范围内的最高水平。

图: SPAD 像素支持捕获极暗的场景,同时还支持捕获明亮的场景且不会出现饱和。

#### 3D 闪存

"采用 3.2Gbps 接口且程序吞吐量为 205MB/s、位密度超过 17Gb/mm² 的 1Tb 3b/单元 3D 闪存"——错侠公司(论文 C2-1)

铠侠公司报告了 210 多个字线层 1Tb 3b/单元 3D 闪存,位密度超过 17Gb/mm²。8 个平面的物理架构实现了 40ms 的低读取延迟和 205MB/s 的高程序吞吐量。通过将 X 方向的 DQ 面积减少到 41%,实现了 3.2Gbps 的高接口速度。混合行地址解码器(X-DEC)可以处理由新架构引起的布线拥塞问题,从而最大限度地减少读取延迟性能的下降。单脉冲双选通技术可将检测时间缩短 18%,并帮助实现 205MB/s 的程序吞吐量。

图: 1Tb 3D 闪存的芯片显微照片。

#### SRAM 存储器

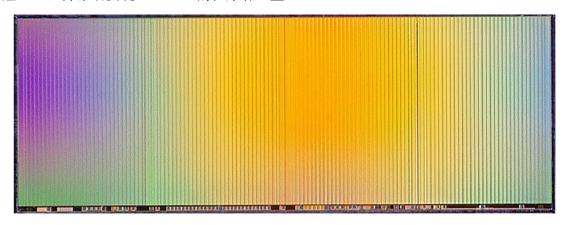

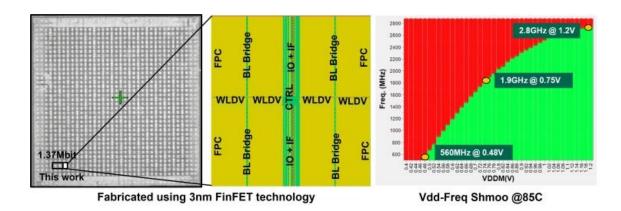

"搭载远端预充电和弱位跟踪且实现 0.48-1.2 V 宽工作范围的 3 nm 27.6 Mbit/mm² 自定时 SRAM"——TSMC Design Technology Japan (论文 C9-5)

台积电推出采用 3nm 鳍式场效应晶体管技术的高能效缓存 SRAM。高性能计算系统对电源效率提出了很高的要求。DVFS 广泛用于最近的设计中,以提高电源效率。在这种 DVFS 系统中,无论是较高过驱动电压下的高速运行还是极低电压下的绿色电源运行,都非常需要片上缓存存储器。文中还介绍了两个新的 DTCO。一个是远端位线预充电电路,另一个是弱位跟踪电路,支持宽电压范围和细粒度 DVFS。推出的 DTCO 提高了性能,可应对 1)接线电阻的增加;和2)晶体管特性的电压相关灵敏度的增加,二者都是尖端技术面临的挑战。测试芯片采用 3nm 鳍式场效应晶体管技术制造,在 0.48V 至 1.2V 宽电压范围内具有 27.6Mbit/mm²的高密度和550MHz 至 2.8GHz 的工作频率,FoM(=密度 x Fmax/VDD)为历来最佳。

图:制造的 3nm 鳍式场效应晶体管测试芯片的芯片照片、434kbit SRAM 宏的布局图以及测量的电压-频率 shmoo 图。

# 神经接口

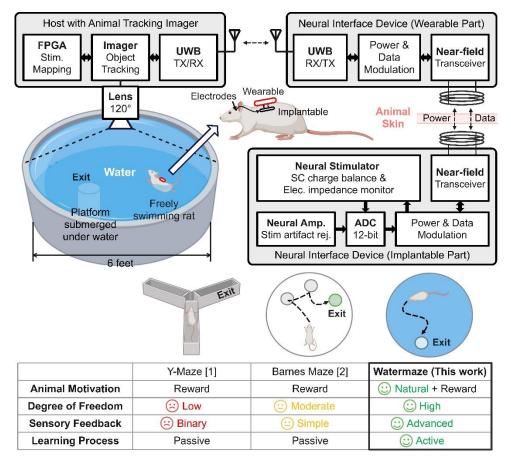

"通过目标导向闭环神经调控跟踪和指导动物行为的无线传感脑机接口"——多伦多大学(论文C1-1)

多伦多大学报告了一种无线大脑刺激系统,该系统能够使用实时生成的脑刺激将水迷宫中的啮齿动物引至目标。该系统配备了一个基于 FPGA、带有 160 x 160 图像传感器的控制主机,这是一个由完全植入和可穿戴部件组成的无线神经接口设备。该主机跟踪水迷宫中的大鼠,并产生刺激模式进行引导。作者成功地证明,与视觉上可以看到目标的对照实验一样,老鼠可以在大脑刺激的帮助下快速到达水迷宫中的淹没目标。

图: 传感器-脑机接口系统的框图以及使用水迷宫进行演示的有效性。

#### 生物医学电路

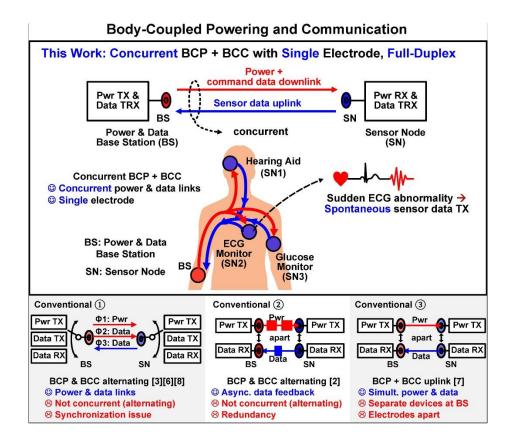

"采用单电极并发体耦合供电和通信的无线体域网收发器 IC"——南方科技大学(论文 C8-1)

作者开发了一种BAN收发器IC,该IC利用单个电极为每个传感器节点提供电源和数据通信,以便通过安装在人体上的基站和多个传感器节点连续监测医疗保健信息。当电力传输和通信同时处于活动状态时,来自基站上电力传输电路的干扰会使接收电路饱和,因此采用了抑制性能超过 40dB 的自干扰消除电路来解决这个问题。传感器节点电路通过将电源/数据接收部分的接地与数据传输部分的接地分开,实现稳定的功率接收。

图: 使用单电极同时进行经人体的电力传输和数据通信的概念

#### 生物医学电路

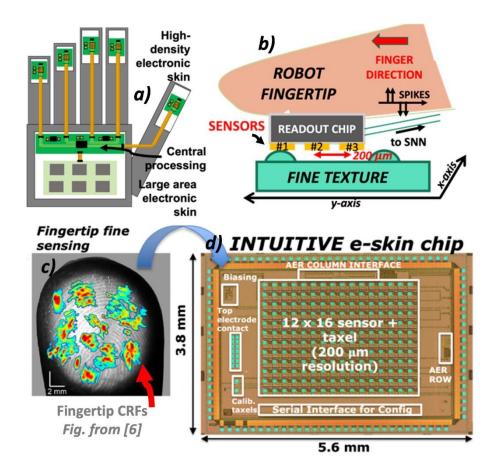

"提供每 Taxel 尖峰读数和嵌入式感受野处理的指尖模拟 12x16 200um 分辨率电子皮肤 Taxel 读数芯片"——KU Leuven (论文 C8-2)

KU Leuven 报告了采用 0.18μm CMOS 技术的电子皮肤(e-skin)taxel 读数芯片,实现了 200μm 的历史最高空间分辨率,可与人类指尖相媲美。一项关键创新是将 12×16 taxel 阵列与每 taxel 信号调节前端和尖峰读数集成在芯片上,并与通过复杂感受野(CRF)进行的嵌入式神经形态一阶处理相结合。与旧式的电子皮肤技术相比,这项工作使系统功耗降低约 100-7000 倍,每 taxel 功耗降低>5 个数量级,同时将空间分辨率提高了 5 倍,并将传感器的数量增加了一倍。实验结果表明,基于尖峰神经网络(SNN)对输入触觉刺激(如纹理和颤振频率)的芯片时空尖峰输出进行分类,分别实现了高达 97.1%和 99.2%的分类精度。

图:模仿人类指尖触觉的电子皮肤芯片。芯片安装在机器人的手掌和指尖上。

#### 数字电路

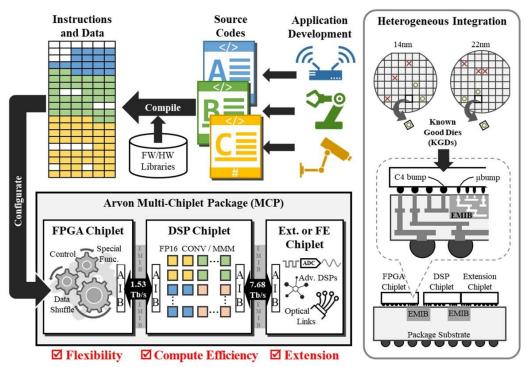

"Arvon: 搭载一个14nm FPGA、两个22nm 1.8TFLOPS/W DSP 和1.7Tbps/mm2 AIB 2.0 接口的异构SiP 可提供多功能工作负载加速"——密歇根大学(论文 C7-1)

密歇根大学的研究人员与英特尔合作,报告了一种异构系统级封装(SiP),通过嵌入式多芯片互连桥(EMIB)将一个 14nm FPGA 芯粒与两个 22nm DSP 芯粒集成在一起。芯粒通过高级接口总线(AIB)1.0接口和 AIB 2.0接口进行通信。SiP 演示了有史以来第一个使用 36μm 间距微凸块的 AIB 2.0 I/O 原型,在 0.10pJ/b(包括适配器在内为 0.46pJ/b)时实现了 4Gbps/引脚。SiP 是可编程的,支持从神经网络(NN)到通信处理(comm)的工作负载,并提供4.14TFLOPS(FP16,半精度浮点)的峰值性能。他们开发了一个编译流程,用于跨 FPGA 和DSP 映射工作负载,以优化性能和利用率。

\*FE: front-end; \*EMIB: Embedded Multi-die Interconnect Bridge; \*MMM: matrix-matrix multiplication; \*AIB: Advanced Interface Bus

图: Arvon SiP 异构集成 FPGA、DSP、FE 芯粒,实现灵活的工作负载映射。

# 有线接收机

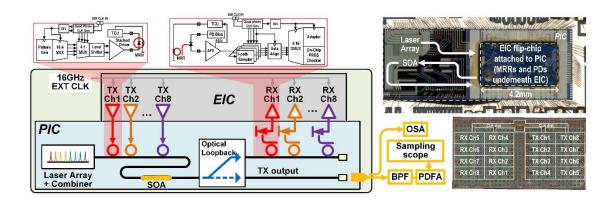

"面向封装内光学 I/O 基于基异构集成硅光子微环的 256 Gbps DWDM 接收机"——英特尔公司(论文 C6-2)

英特尔提出了基于异构集成硅光子微环的密集波分复用(DWDM)接收器。基于抖动的热控制单元可调谐光学解复用器中的微环谐振器,以亚 pm 级分辨率与激光网格对齐。收发器的实现形式为堆叠在硅光子 IC 上的 28nm CMOS 电子 IC。它通过使用间隔统一为 200GHz 的 8 个波长,在 256 Gbps 实现了 BER<1e-12、3.6 dBm 的光功率和 3.8 pJ/b 的能效。

图: 异构集成的密集波分复用(DWDM)收发器,具有电子IC和光子IC细节。收发器组件和电子IC的照片。

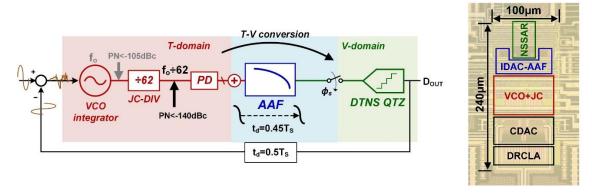

# 模数转换器

"搭载 NS-SAR 量化器 (NSQ VCO CTDSM)、基于 VCO 的 0.024mm<sup>2</sup> 84.2dB-SNDR 1MHz-BW 3 阶 CTDSM"——密歇根大学(论文 C4-2)

密歇根大学提出了一种新的混合 ADC 架构,该架构使用了搭载噪声整形(NS)SAR 量化器、基于 VCO 的连续时间  $\Delta$ -Σ 调制器(DSM)。将 VCO 前端桥接于 NS SAR 的抗混叠滤波器,使时域信息能够作为电压域信息被直接采样。该 28nm CMOS 原型在 1MHz 带宽内实现了 84.2dB SNDR 和 86.8dB DR,同时在 100MS/s 下的功耗为 1.62mW。

图: 新的混合 ADC 架构(其搭载的抗混叠滤波器可将 VCO 前端与 NS SAR 桥接)和 28nm CMOS 原型的芯片图。

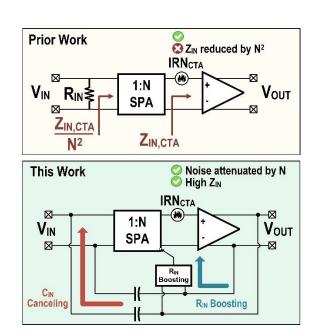

# 模拟技术

"实现0.34 噪声效率因子和 $389 M\Omega$ 输入阻抗的高能效高输入阻抗离散时间放大器"——苏黎世联邦理工学院(论文C19-2)

苏黎世联邦理工学院的研究人员展示了一种用于低功耗传感器系统的高噪声效率模拟前端(AFE)。所提出的 AFE 采用基于串联-并联转换器的低噪声放大器,其输入阻抗通过输入电阻升压环路和容性正反馈环路增大至 389  $M\Omega$ 。与先前的工作相比,这种提升阻抗的技术带来了 39 倍的性能改进。AFE 的噪声效率因子和功率效率因子分别为 0.34 和 0.1,为历史最低,功耗为 370nW。

图: 提升输入阻抗的模拟前端架构以及与传统架构的比较。

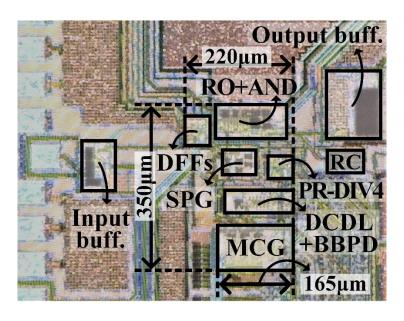

# 频率发生器

"使用功率门控技术、具有102 倍增因子、122fsrms 抖动和-60dBc 参考杂散的12.24GHz MDLL"——韩国科学技术院(论文 C26-5)

韩国科学技术院提出了一种具有低抖动和 12.24GHz 输出的时钟倍增器。其采用环形振荡器式倍增器来节省布局面积,面积仅 0.066mm²。使用传统环形振荡器式倍增器很难提高输出频率,但所提出的门控技术实现了更高的频率输出。此外,内置的校准电路可将参考杂散降至-60 dBc。

图: 低抖动和 12.24GHz 输出紧凑型时钟倍增器